Secure Your SoC's Data Integrity with Hardware-Enforced Memory Protection

- Stop Data Breaches: Isolate highly critical memory regions

- Achieve Functional Safety: Designed to support ASIL B and D certification

- Maximize Throughput: Fully pipelined, Single-cycle operation

- Reduce Integration Risk: Tape-out ready and UVM-verified

Key Highlights

RISC-V Compliant

Advanced Process

Multiple Models

Protect Your SoC from Rogue I/O Transactions

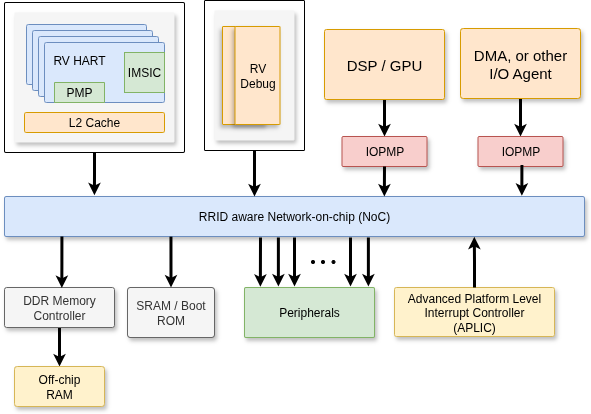

Modern SoCs integrate numerous masters – GPUs, NPUs, DMAs and peripherals – each capable of accessing system memory. A single compromised or misbehaving master can expose the entire system to data leaks or catastrophic failures.

- The Risk

- The Need

The Solution: 10xEngineers RISC-V IOPMP IP

Our Input/Output Physical Memory Protection (IOPMP) IP integrates directly into your SoC interconnect, providing hardware-level validation of every memory transaction against programmable access rules. Unauthorized transactions are blocked instantly — ensuring security without latency penalties.

Why Choose 10xEngineers IOPMP IP?

-

Fully Spec-Compliant

Implements all mandatory and optional features of RISC-V IOPMP Specification v0.8 -

Tape-Out Proven

Synthesized, verified, and production-ready for advanced process nodes -

Highly Configurable

Multiple pre-verified configurations for different area, feature, and performance goals -

UVM-Verified

Delivered with full verification suite and coverage closure for maximum reliability

System Integration

Key Features & Benefits

Granular Access Control

- Supports OFF, NA4, TOR, and NAPOT address matching with 4B granularity

- Up to 64 Requestor IDs mapped to Memory Domains for flexible partitioning

Robust Security

- Lockable domains prevent runtime modification

- Atomic updates eliminate transient security gaps

- Secondary permissions enable controlled sharing across requestors

Advanced Debug & Safety

- Real-time violation alerts and detailed error logging

- MSI/WSI interrupt support and multi-fault records for traceability

- Built-in features to support functional safety compliance

High-Performance Architecture

- Fully pipelined, single-cycle throughput

- Deterministic latency (~26 cycles per transaction check)

- Optimized for 1GHz+ operation in 12nm technology

Choose Your Configuration

Our IOPMP IP family offers flexible configurations to match your area, performance, and feature requirements. All models are pre-verified using full UVM testbenches.

| Feature | Full Model Maximum Security | Rapid-2 Model Fast Rule Checks | WgC Model High Security | Full Model Lite Balanced Features | Rapid-2 Model Lite Area-Constrained |

|---|---|---|---|---|---|

| Max Entries / MDs | 128 / 63 | 126 / 63 | 128 / 63 | 128 / 31 | 62 / 31 |

| Max RRIDs | 64 | 64 | 32 | 24 | 24 |

| Address Modes | OFF, NA4, TOR, NAPOT | OFF, NA4, TOR, NAPOT | OFF, NA4, TOR, NAPOT | OFF, NA4, NAPOT | OFF, NA4, NAPOT |

| Multi-Fault Record | |||||

| Secondary Permissions | |||||

| Priority Entries | Up to 48 (Prog) | Up to 48 (Prog) | Up to 48 (Prog) | Up to 48 (Fixed) | Up to 16 (Fixed) |

| Locking Options | MDCFG, MD, Entry | MD & Entry | MDCFG, MD, Entry | Entry | MD & Entry |

Performance, Power & Area Metrics

Synthesized in 12nm process technology, targeting 1GHz operation

1 GHz

Target Frequency

All models achieve timing closure

13.5-22.7kGE

Area

40% area reduction in Lite models

271-373 mW

Power

@1GHz operation

~26 cycles

Latency

Deterministic operation

Area Comparison Across Models

Detailed PPA Analysis

| Model | Area (kGE)* | Total Power (mW) | Relative Area | Best For |

|---|---|---|---|---|

| Full Model | 22.67 | 373.41 | Reference | High-security applications |

| Rapid-2 Model | 20.90 | 369.61 | -8% | Fast rule checking |

| WgC Model | 18.30 | 325.43 | -19% | High-security applications |

| Full Model Lite | 16.13 | 303.75 | -29% | Cost-sensitive designs |

| Rapid-2 Model Lite | 13.52 | 271.06 | -40% | Area-constrained designs |

PPA Trade-off Analysis

Performance

Area Efficiency

Power Efficiency

- Technical Note

Accelerate Your Development

Synthesizable RTL

Lint-clean, CDC-ready RTL code for immediate integration into your design flow

Comprehensive Verification Suite

UVM testbench with full coverage to ensure reliability and compliance

Detailed Integration Guide

Verification IP & Cover Properties

Shell RTL & Smoke Tests

Technical Support

Expert assistance during integration and deployment phases